## EE 330 Lecture 7

- Propagation Delay

- Stick Diagrams

- Technology Files

- Design Rules

As a courtesy to fellow classmates, TAs, and the instructor

Wearing of masks during lectures and in the laboratories for this course would be appreciated irrespective of vaccination status

#### Review from Last Time

## **Complex Gates**

#### **Complex Gate Design Strategy:**

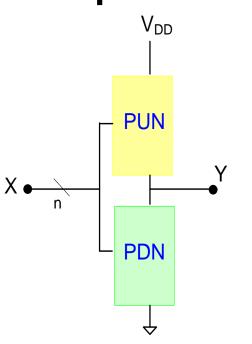

1. Implement  $\overline{\gamma}$  in the PDN

2. Implement Y in the PUN (must complement the input variables since pchannel devices are used)

(Y and  $\overline{Y}$  often expressed in either SOP or POS form)

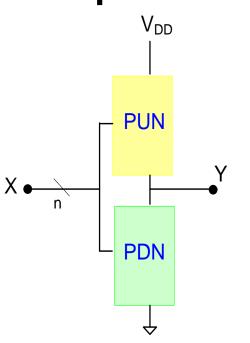

# **Review from Last Time** Complex Logic Gate Summary: PUN PDN

If PUN and PDN satisfy the characteristics:

- 1. PU network comprised of p-channel device

- 2. PD network comprised of n-channel device

- 3. One and only one of these networks is conducting at the same time

**Properties of PU/PD logic of this type** (with simple switch-level model):

Rail to rail logic swings Zero static power dissipation in both Y=1 and Y=0 states Arbitrarily fast (too good to be true? will consider again with better model)

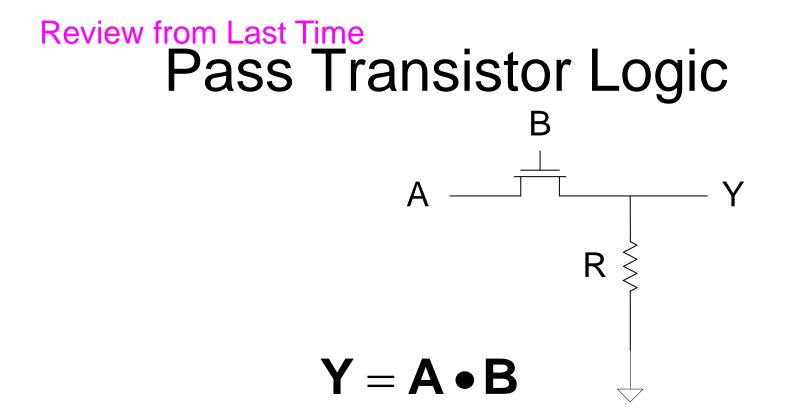

## Pass Transistor Logic

- Pass transistor logic can offer significant reductions in complexity for some functions (particularly noninverting)

- Resistor may require more area than several hundred or even several thousand transistors

- Signal levels may not go to  $V_{\text{DD}}$  or to 0V

- Static power dissipation may not be zero

- Signals may degrade unacceptably if multiple gates are cascaded

- -"resistor" often implemented with a transistor to reduce area but signal swing and power dissipation problems still persist

- Pass transistor logic is widely used

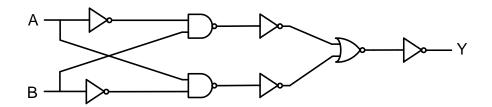

#### Review from Last Time Example 2: XOR Function

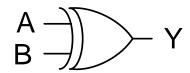

A widely-used 2-input Gate

**Static CMOS implementation**

$Y = A\overline{B} + \overline{A}B$

22 transistors 5 levels of logic

Delays unacceptable (will show later) and device count is too large !

## Review from Last Time Complex Gates

#### **Complex Gate Design Strategy:**

1. Implement  $\overline{Y}$  in the PDN

2. Implement Y in the PUN (must complement the input variables since pchannel devices are used)

(Y and  $\overline{Y}$  often expressed in either SOP or POS form)

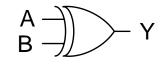

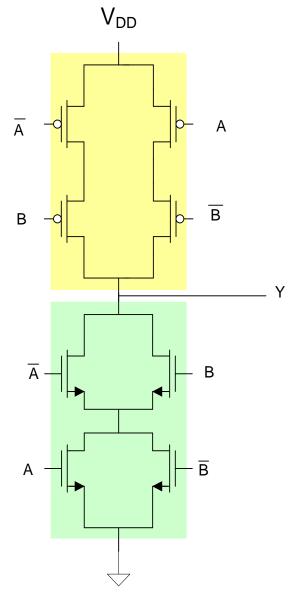

# XOR in Complex Logic Gates

$$\overline{Y} = (\overline{A} + B) \cdot (A + \overline{B})$$

$Y = A\overline{B} + \overline{A}B$

12 transistors and 2 levels of logic

Notice a significant reduction in the number of transistors required

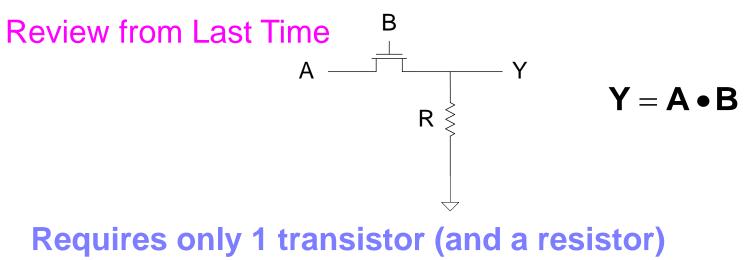

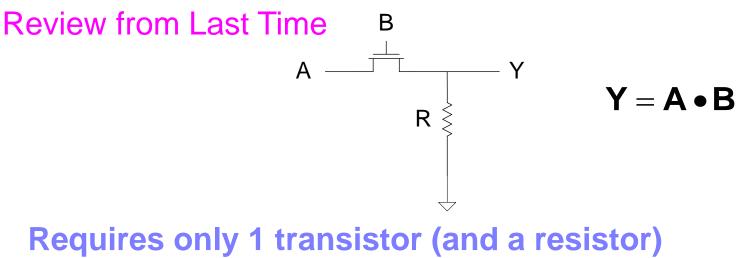

**Even simpler pass transistor logic implementations are possible**

**Requires only 1 transistor (and a resistor).**

Will see later that the area of a single practical resistor for this circuit may be comparable to that needed for hundreds or even thousands of transistors

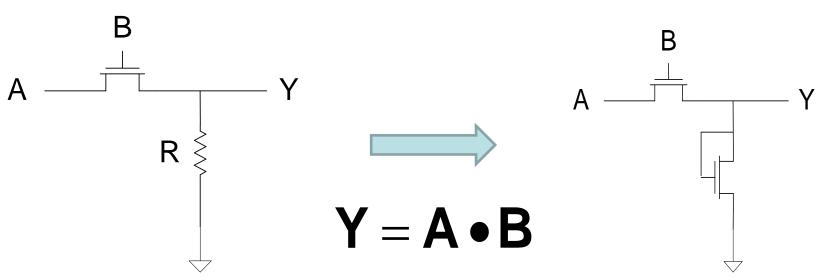

## Review from Last Time Pass Transistor Logic

- May be able to replace resistor with transistor (one of several ways shown)

- But high logic level can not be determined with existing device model (or even low logic level for circuit on right)

- Power dissipation can not be determined with existing device model for circuit on right

Better device model is needed (Power? Signal Swing? Speed?)

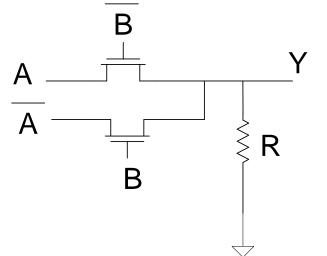

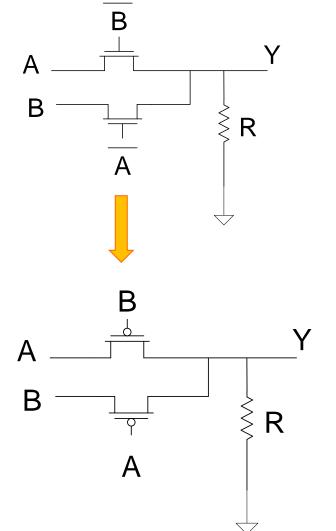

## Review from Last Time Pass Transistor Logic

$\mathbf{Y} = \mathbf{A} \oplus \mathbf{B}$

6 transistors, 1 resistor, two levels of logic

(the 4 transistors in the two inverters are not shown)

### Review from Last Time Pass Transistor Logic

$\mathbf{Y} = \mathbf{A} \oplus \mathbf{B}$

$\mathbf{Y} = \mathbf{A} \oplus \mathbf{B}$

2 transistors, 1 resistor, one level of logic

## Pass Transistor Logic

- Pass transistor logic can offer significant reductions in complexity for some functions (particularly noninverting)

- Resistor may require more area than several hundred or even several thousand transistors

- Signal levels may not go to  $V_{\text{DD}}$  or to 0V

- Static power dissipation may not be zero

- Signals may degrade unacceptably if multiple gates are cascaded

- -"resistor" often implemented with a transistor to reduce area but signal swing and power dissipation problems still persist

- Pass transistor logic is widely used

## Review from Last Time Logic Design Styles

- Several different logic design styles are often used throughout a given design (3 considered thus far)

- Static CMOS

- Complex Logic Gates

- Pass Transistor Logic

- The designer has complete control over what is placed on silicon and governed only by cost and performance

- New logic design strategies have been proposed recently and others will likely emerge in the future

- The digital designer needs to be familiar with the benefits and limitations of varying logic styles to come up with a good solution for given system requirements

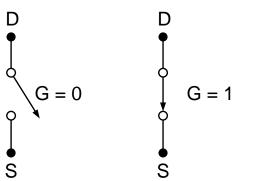

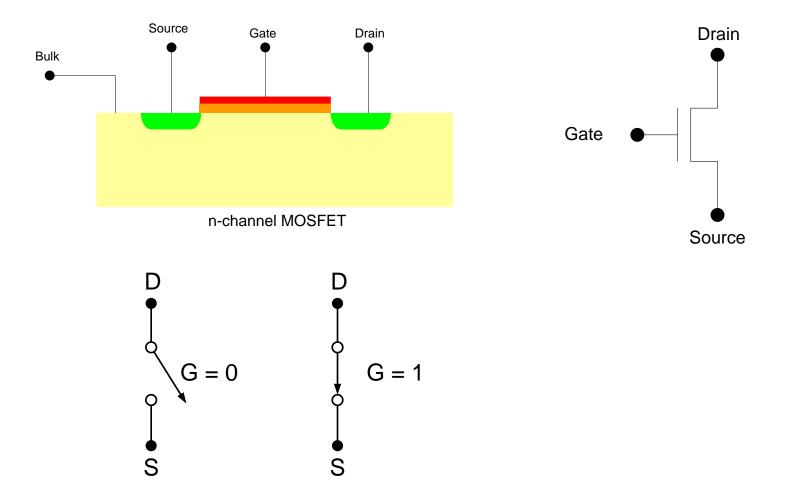

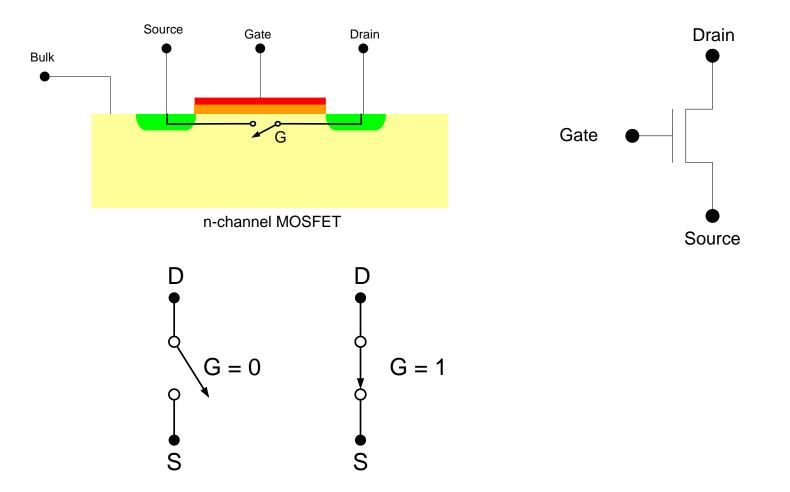

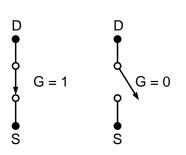

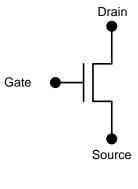

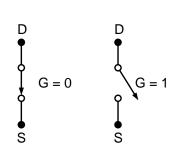

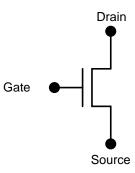

## Review from Last Time MOS Transistor Qualitative Discussion of n-channel Operation

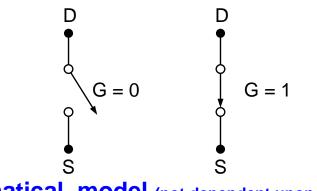

#### Equivalent Circuit for n-channel MOSFET

- Source assumed connected to (or close to) ground

- V<sub>GS</sub>=0 denoted as Boolean gate voltage G=0

V<sub>GS</sub>=V<sub>DD</sub> denoted as Boolean gate voltage G=1

- Boolean G is relative to ground potential

This is the first model we have for the n-channel MOSFET !

Ideal switch-level model

#### Review from Last Time MOS Transistor MODEL

Equivalent Circuit for n-channel MOSFET with source as ground

Mathematical model (not dependent upon Boolean notation):

- Pass Transistor Logic

- Improved Switch-Level Model

- Propagation Delay

- Stick Diagrams

- Technology Files

- Simple model of MOSFET was developed (termed switch-level model)

- Simple gates designed in CMOS Process were introduced

- Some have zero power dissipation

- Some have or appeared to have rail to rail logic voltage swings

- All appeared to be Infinitely fast

- Logic levels of some can not be predicted with simple model

- Simple model is not sufficiently accurate to provide insight relating to some of these properties

- MOSFET modeling strategy

- hierarchical model structure will be developed

- generally use simplest model that can be justified

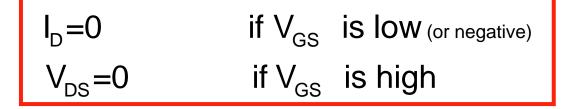

## **MOS Transistor Models**

Advantages:

1,

Switch-Level model

Simple, does not require understanding of semiconductor properties, does not depend upon process, adequate for understanding basic operation of many digital circuits

#### Limitations:

Does not provide timing information (surfaced when looking at static CMOS circuits, and several others that have not yet become apparent from the applications that have been considered) and can not support design of "resistor" used in Pass Transistor Logic

# **Improved Device Models**

With the simple switch-level model, it was observed that basic static CMOS logic gates have the following three properties:

- Rail to rail logic swings

- Zero static power dissipation in both Y=1 and Y=0 states

- Arbitrarily fast (too good to be true? will consider again with better model)

It can be shown that the first two properties are nearly satisfied in actual fabricated circuits with p-channel/n-channel PU/PD logic but though the circuits are fast, they are observably not arbitrarily fast

None of these properties are observed for some logic styles such as Pass Transistor Logic

# Will now extend switch-level model to predict speed of basic gates in static CMOS and logic levels and power dissipation in PTL

Device Models and Operation

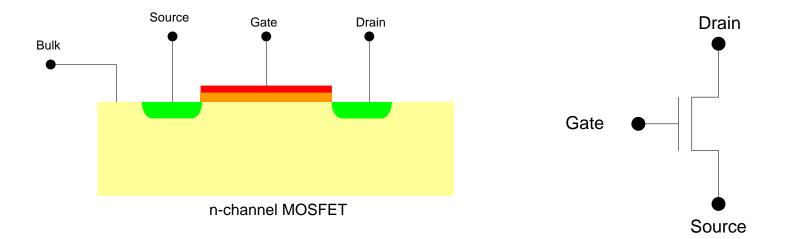

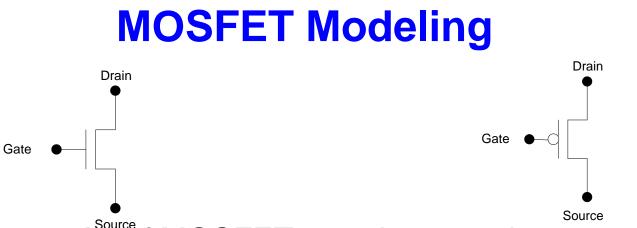

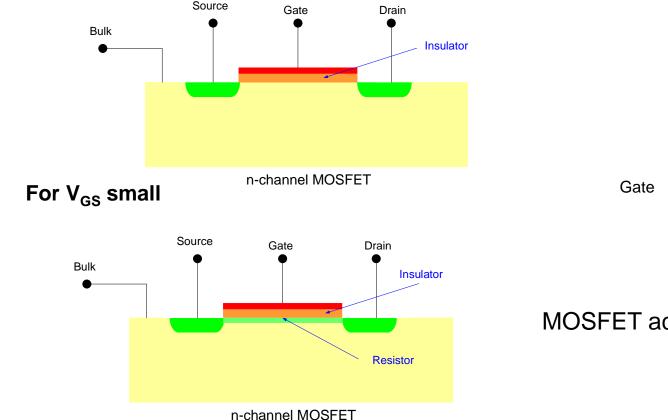

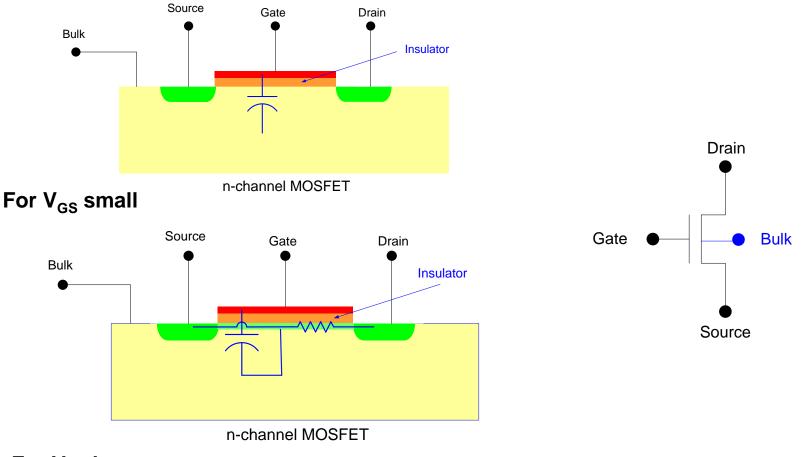

### Recall MOS Transistor Qualitative Discussion of n-channel Operation

This was the first model introduced and was termed the basic switch-level mode

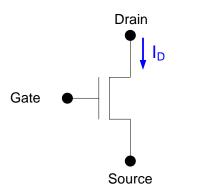

## MOS Transistor Qualitative Discussion of n-channel Operation

#### Conceptual view of basic switch-level model

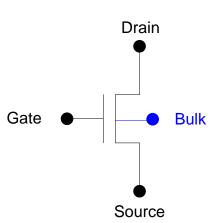

## MOS Transistor Qualitative Discussion of n-channel Operation

#### MOSFET actually 4-terminal device

#### For $V_{GS}$ large

- Region under gate termed the "channel"

- When "resistor" is electrically created, region where it resides in channel is termed an "inversion region"

## MOS Transistor Qualitative Discussion of n-channel Operation

For V<sub>GS</sub> large

- Electrically created inversion layer forms a "thin "film" resistor

- Capacitance from gate to <u>channel region</u> is distributed

- Lumped capacitance much easier to work with

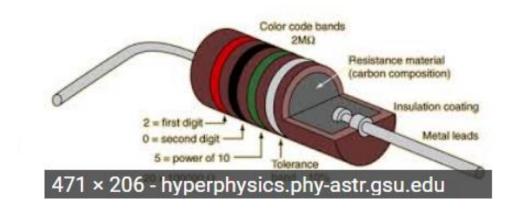

# Discrete Resistors often use thin films too though not electrically created

Thin-film spiral wound

Carbon composition

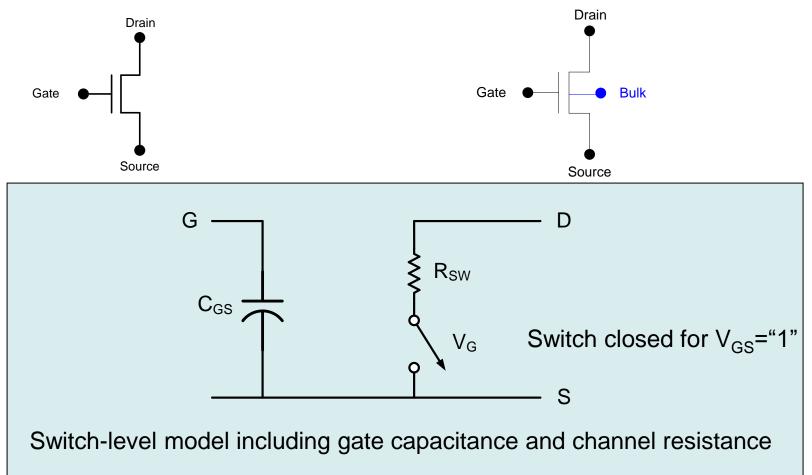

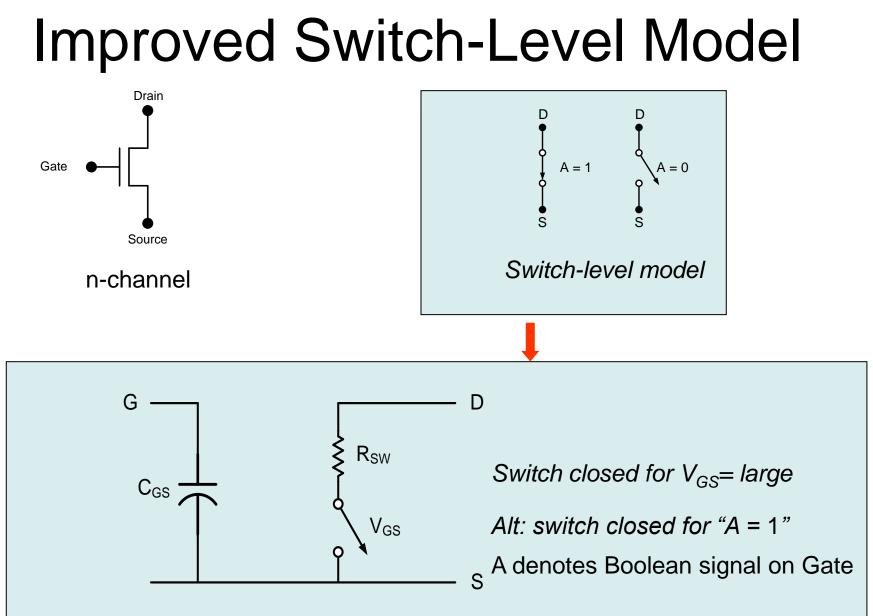

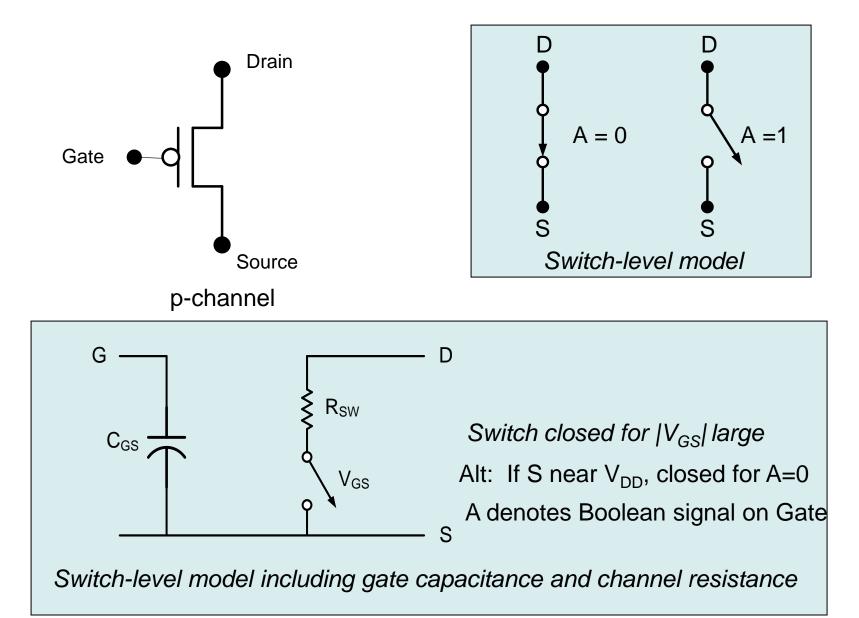

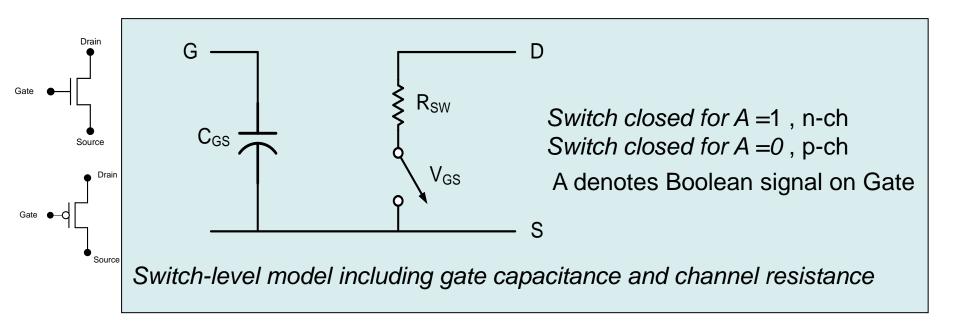

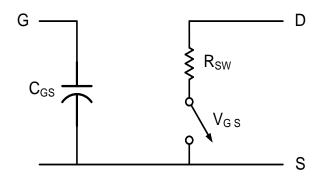

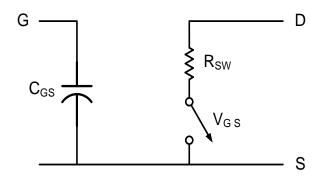

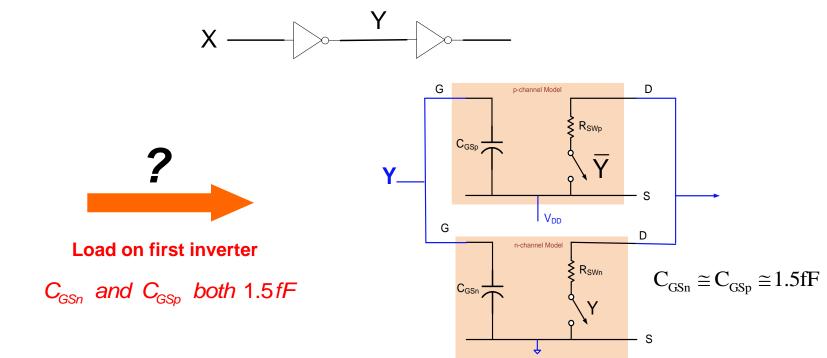

# Improved Switch-Level Model

- Connect the gate capacitance to the source to create lumped model

- Still neglect bulk connection

Switch-level model including gate capacitance and channel resistance

# Improved Switch-Level Model

# Improved Switch-Level Model

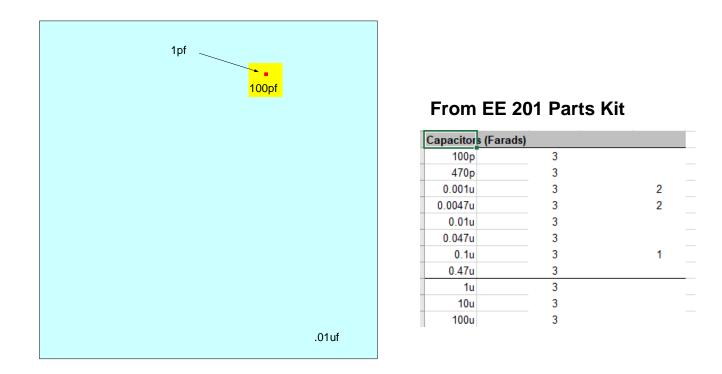

$C_{GS}$  and  $R_{SW}$  dependent upon device sizes and process For minimum-sized devices in a 0.5u process with  $V_{DD}$ =5V  $C_{GS} \cong 1.5 \text{fF}$   $R_{sw} \cong \begin{array}{c} 2K\Omega & n-channel \\ 6K\Omega & p-channel \end{array}$

Considerable emphasis will be placed upon device sizing to manage  $C_{GS}$  and  $R_{SW}$

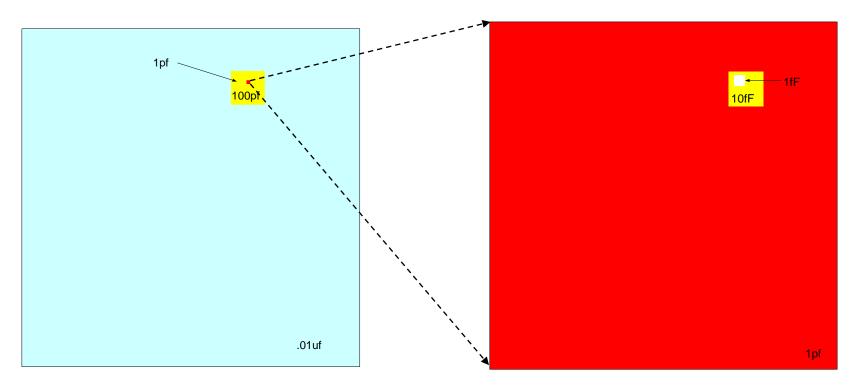

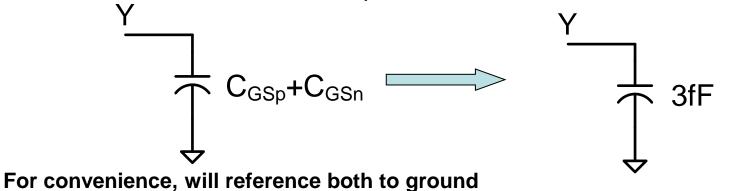

# Is a capacitor of 1.5fF small enough to be neglected?

#### Area allocations shown to relative scale:

# Is a capacitor of 1.5fF small enough to be neglected?

Area allocations shown to relative scale:

- Not enough information at this point to determine whether this very small capacitance can be neglected

- Will answer this important question later

# Model Summary (for n-channel)

1. Switch-Level model

#### 2. Improved switch-level model

Switch closed for  $V_{GS}$ = large Switch open for  $V_{GS}$ = small

#### Other models will be developed later

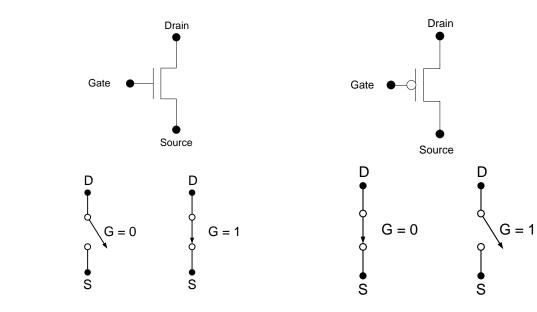

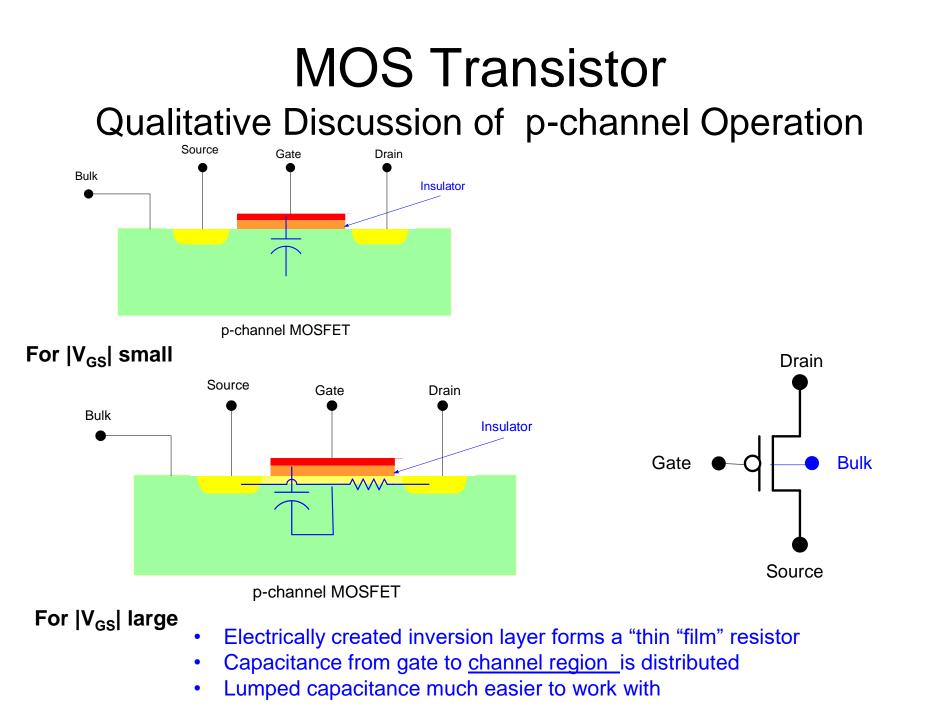

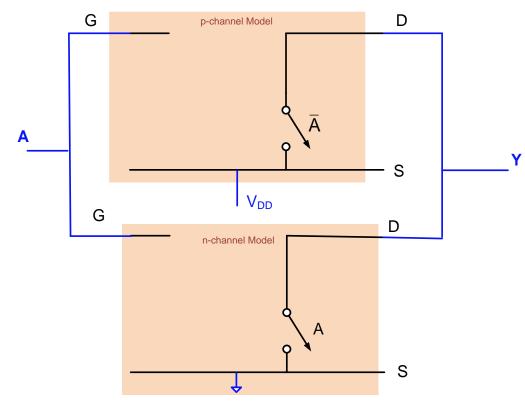

## Model Summary (for p-channel)

1. Switch-Level model

#### 2. Improved switch-level model

Switch closed for  $|V_{GS}|$ = large Switch open for  $|V_{GS}|$ = small

#### Other models will be developed later

Source

Gate •---C

- Pass Transistor Logic

- Improved Switch-Level Model

- Propagation Delay

- Stick Diagrams

- Technology Files

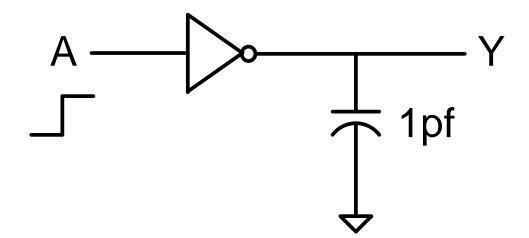

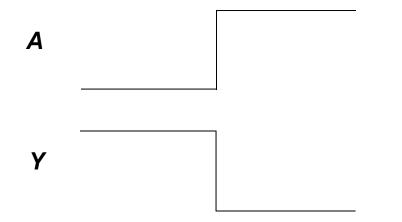

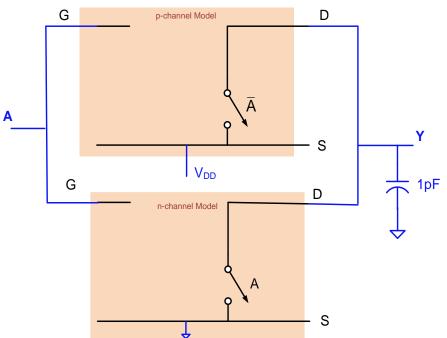

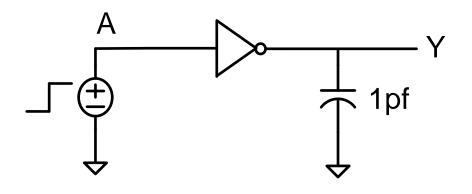

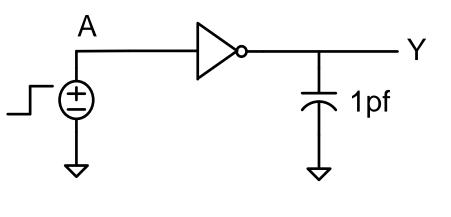

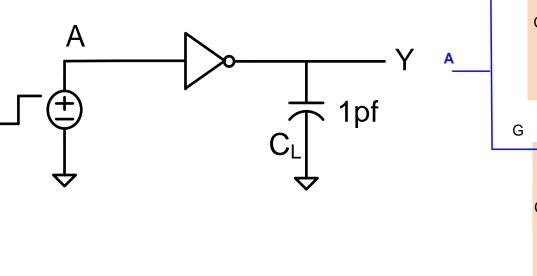

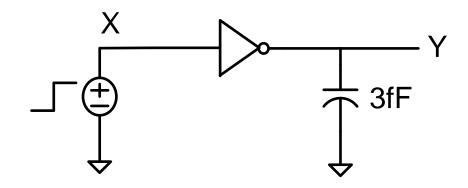

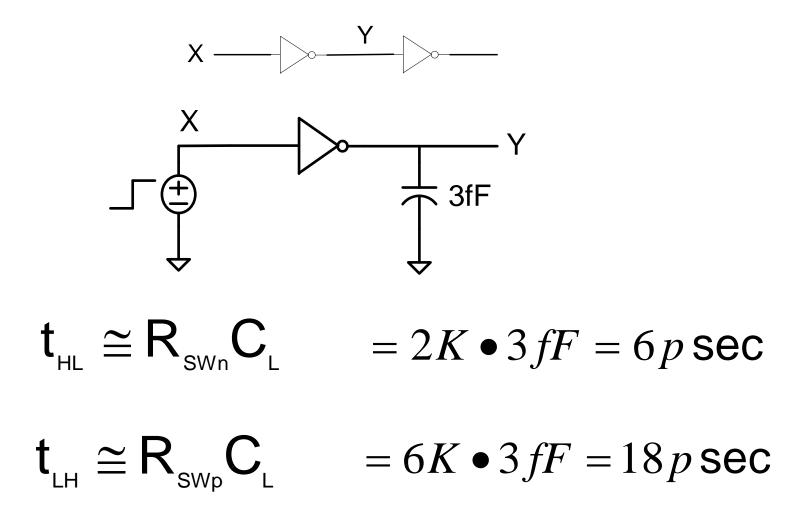

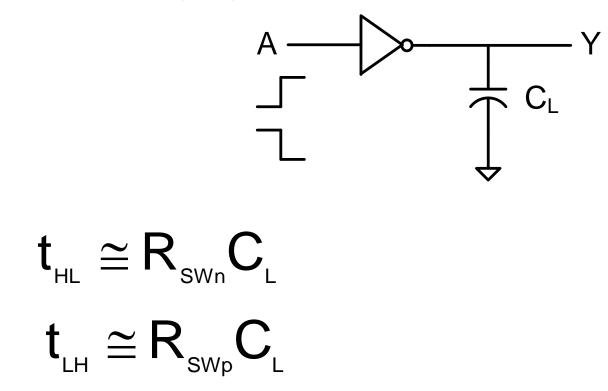

## Example What are t<sub>HL</sub> and t<sub>LH</sub>?

Assume V<sub>DD</sub>=5V

With basic switch level model ?

With improved switch level model?

# Example

#### Inverter with basic switch-level model

# Example What are t<sub>HL</sub> and t<sub>LH</sub>?

With basic switch level model

t<sub>HL</sub>=t<sub>LH</sub>=0

With simple switch-level model  $t_{HL}=t_{LH}=0$

With improved model ?

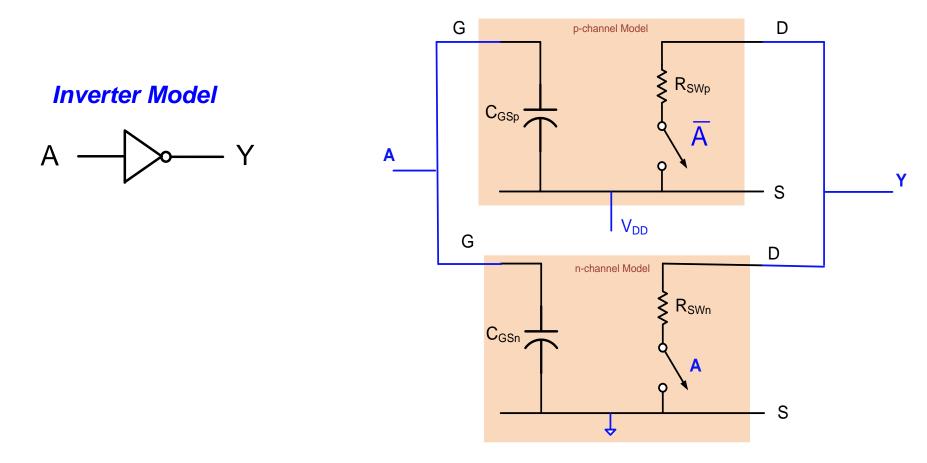

#### Inverter with improved model

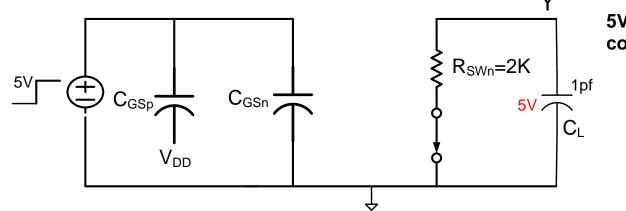

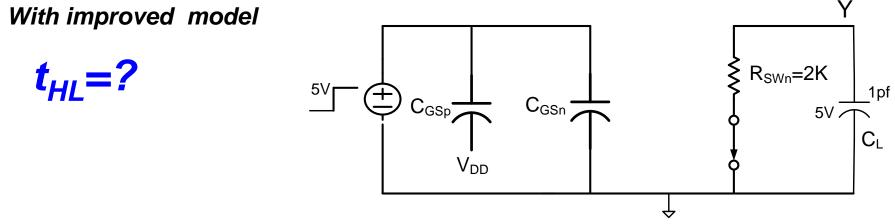

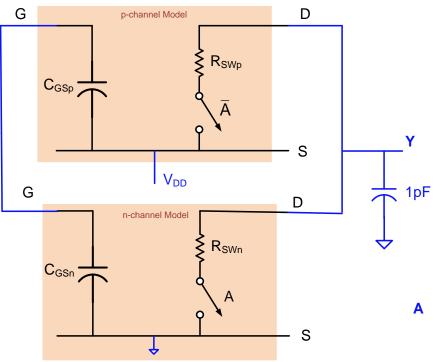

#### **Inverter with Improved Model**

With improved model **t<sub>HL</sub>=?**

To initiate a HL output transisition, assume Y has been in the high state for a long time and lower switch closes at time t=0

5V is the initial condition on  $C_L$

Recognize circuit as a first-order RC network

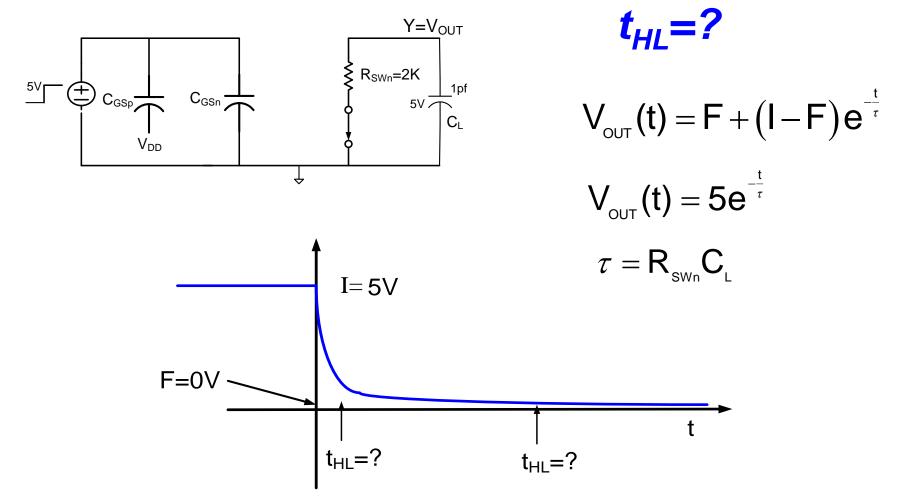

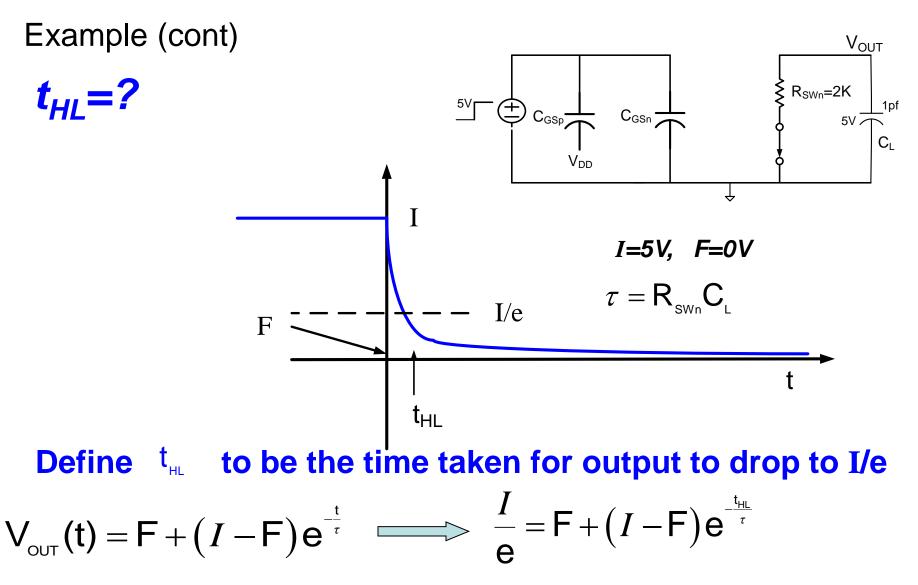

Recall: Step response of any first-order network with LHP pole can be written as

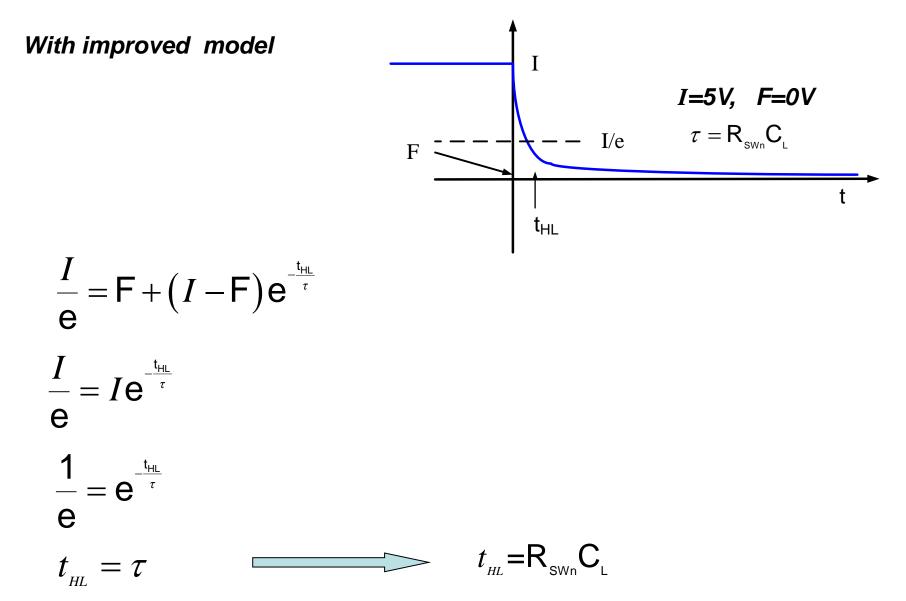

$$\mathbf{y}(\mathbf{t}) = \mathbf{F} + (\mathbf{I} - \mathbf{F})\mathbf{e}^{-\frac{1}{\tau}}$$

where F is the final value, I is the initial value and T is the time constant of the circuit

(from Chapter 7 of Nilsson and Riedel)

For the circuit above, F=0, I=5 and  $\tau = R_{swn}C_{L}$

#### With improved model

how is t<sub>HL</sub> defined?

t<sub>HL</sub> as defined here has proven useful at analytically predicting response time of circuits

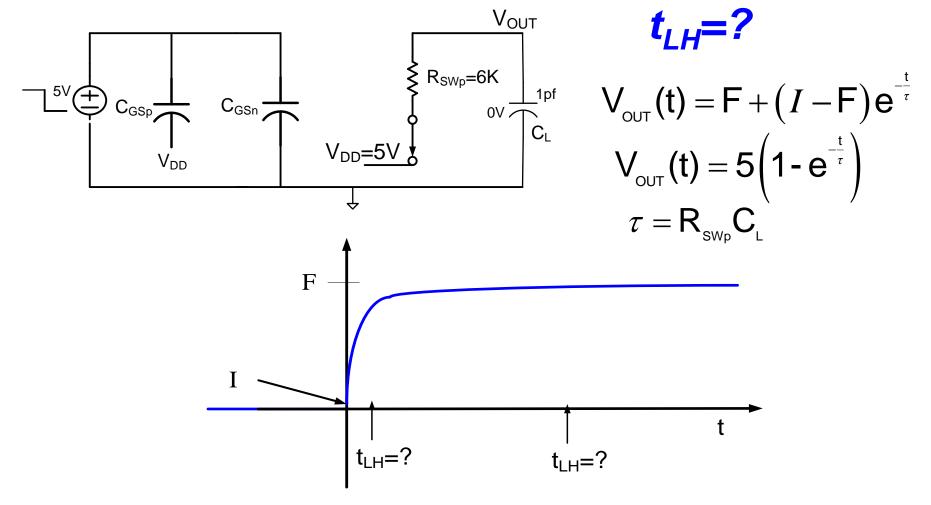

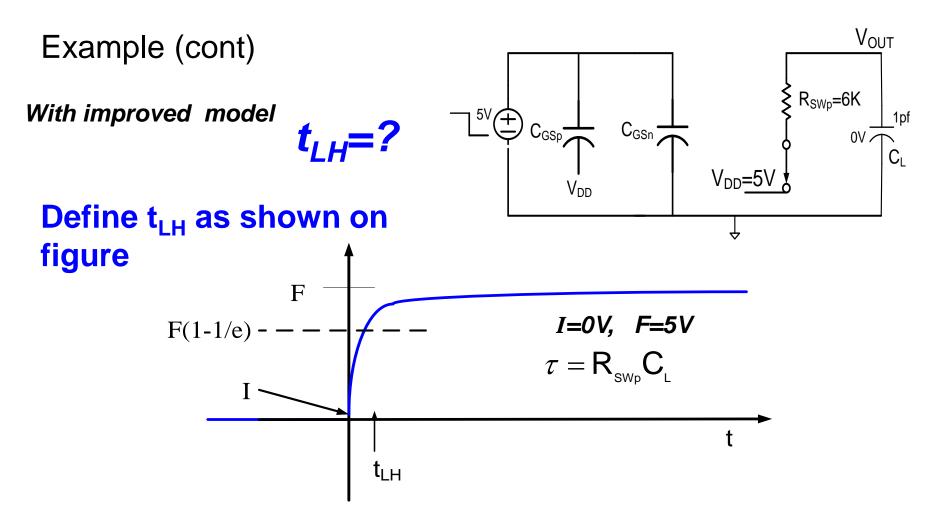

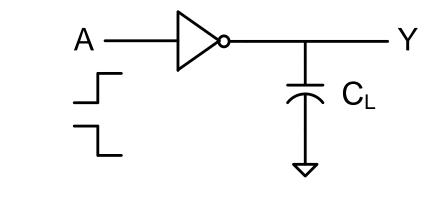

### With improved model t<sub>I H</sub>=?

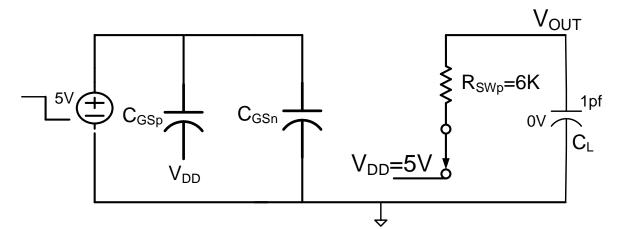

Assume output in low state for a long time and upper switch closes at time t=0

0V is the initial condition on  $C_L$

$$y(t) = F + (I - F)e^{-\frac{t}{\tau}}$$

For this circuit, F=5, I=0 and  $= R_{swp}C_{L}$

With improved model

how is t<sub>LH</sub> defined?

*t<sub>LH</sub>* as defined has proven useful for analytically predicting response time of circuits

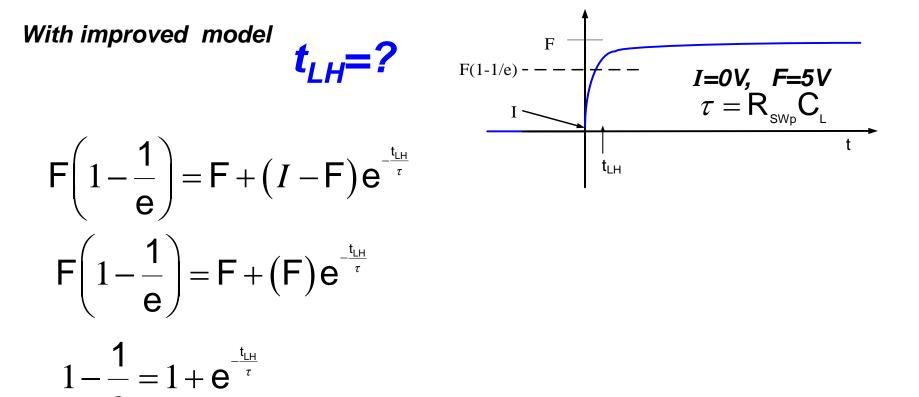

$$V_{out}(t) = F + (I - F)e^{-\frac{t}{\tau}} \qquad \Longrightarrow \qquad F\left(1 - \frac{1}{e}\right) = F + (I - F)e^{-\frac{t_{LH}}{\tau}}$$

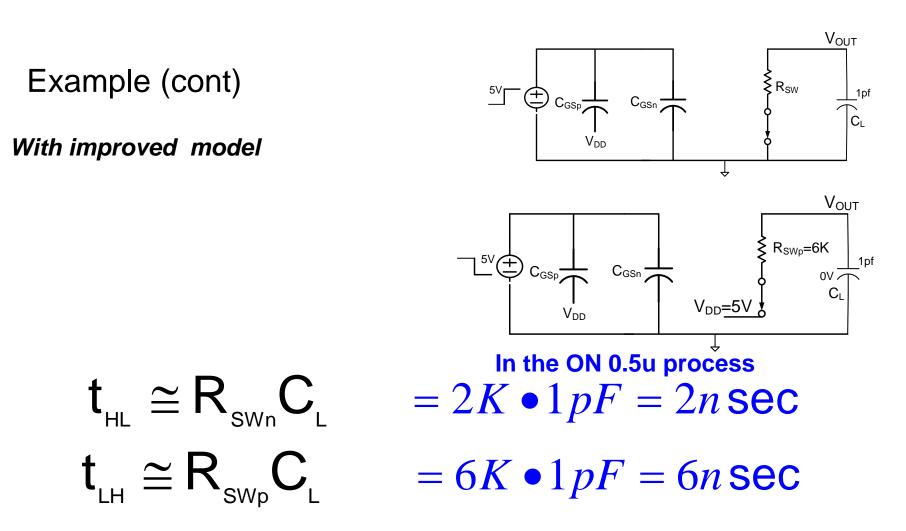

$\mathbf{t}_{_{\mathrm{LH}}} = \tau$

$t_{IH} = R_{SW_D}C_I$

Note this circuit is quite fast !

Note that t<sub>HL</sub> is much shorter than t<sub>LH</sub>

Often C<sub>L</sub> will be even smaller and the circuit will be much faster !!

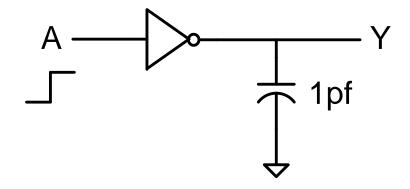

Summary: What is the delay of a minimum-sized inverter driving a 1pF load?

# Improved switch-level model

Switch closed for V<sub>GS</sub>= large

Switch open for  $V_{GS}$  = small

- Previous example showed why R<sub>sw</sub> in the model was important

- But of what use is the C<sub>GS</sub> which did not enter the previous calculations?

For minimum-sized devices in a 0.5µ process

$$\label{eq:GS} \mathbf{C}_{\mathsf{GS}} \cong \mathbf{1.5} \mathbf{f} \mathbf{F} \qquad \mathsf{R}_{\mathsf{sw}} \cong \begin{array}{c} \mathsf{2} \mathsf{K} \Omega \quad \mathsf{n} - \mathsf{channel} \\ \mathsf{6} \mathsf{K} \Omega \quad \mathsf{p} - \mathsf{channel} \end{array}$$

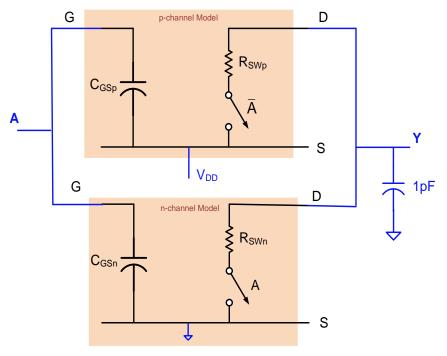

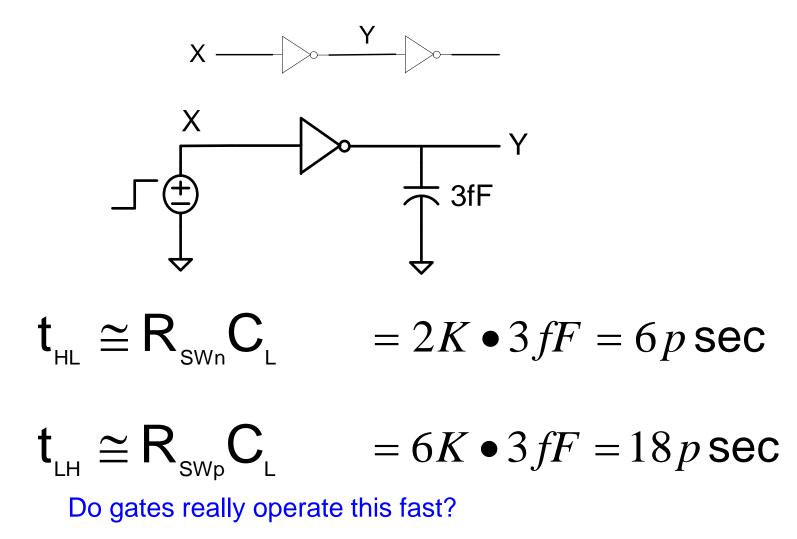

### One gate often drives one or more other gates !

What are t<sub>HL</sub> and t<sub>LH</sub>?

Example: What is the delay of a minimum-sized inverter driving another identical device?

Loading effects same whether  $C_{GSp}$  and/or  $C_{GSn}$  connected to  $V_{DD}$  or GND

# Is a capacitor of 1.5fF small enough to be neglected?

# Area allocations shown to relative scale:

This example will provide insight into the answer of the question Example: What is the delay of a minimum-sized inverter driving another identical device? Assume  $V_{DD}=5V$

Generalizing the Previous Analysis to Arbitrary Load

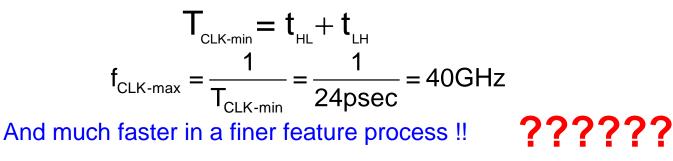

$t_{\rm HL} \cong R_{\rm SWn}C_{\rm L}$  $t_{\rm LH} \cong R_{\rm SWp}C_{\rm L}$

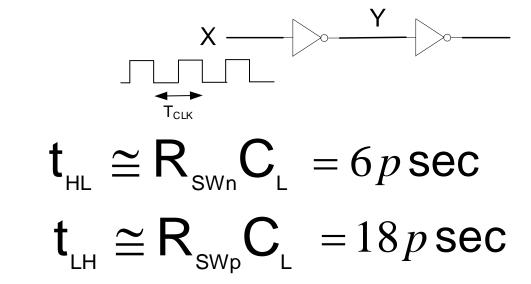

Example: What is the delay of a minimum-sized inverter driving another identical device?

What would be the maximum clock rate for acceptable operation?

Example: What is the delay of a minimum-sized inverter driving another identical device?

What would be the maximum clock rate for acceptable operation?

What would be the implications of allowing for 10 levels of logic and 10 loads (FanOut=10)?

Example: What is the delay of a minimum-sized inverter driving another identical device? SUMMARY

Note this is very fast but even the small 1.5fF capacitors are not negligable !

Response time of logic gates

- Logic Circuits can operate very fast

- Extremely small parasitic capacitances play key role in speed of a circuit

Technology discussions and laboratory designs in this course will be in an ON 0.5µm process

This technology was State of the Art in about 1995 (25 years ago!)

State of the Art today is about 7nm

**Technology Evolution:**

1μm, 0.5μm, 0.35, 0.5μm, 0.18 μm , 0.1μm, 90nm, 65nm, 45nm, 28nm, 22nm, 14nm, 10nm, 7nm

11 generations since the 0.5µm process was at the State of the Art

When 0.5µm processes were state of the art, most US researchers and most universities were working with the state of the art processes or maybe one generation behind the state of the art

**Technology Evolution:**

1μm, 0.5μm, 0.35, 0.5μm, 0.18 μm , 0.1μm, 90nm, 65nm, 45nm, 28nm, 22nm, 14nm, 10nm, 7nm

Students at universities in Asia and Europe often have ready access to technologies in the 14nm to 28nm realm

Are we using obsolete technology in US Universities Today?

Why do we not have ready access to "state of the art" technologies in US Universities?

Will students trained with 25 year old technologies be able to work with state of the art technologies?

Are the larger feature size technologies still used by industry today in the US or abroad?

US Government has recognized that investment in the semiconductor industry is critical to regain technical dominance in the field

The US is now in a serious catchup position because except for Intel, US technology is now about a decade behind foreign competitors

# A recent announcement looks promising for the future !

https://www.washingtonpost.com > 2021/06/14 > global...

Senate approved \$52 billion in subsidies for chip manufacturing

Will this investment close the gap that exists today in semiconductor technology or actually reverse the world order in the semiconductor industry?

Will this \$52 Billion investment by US Government close the gap that exists today in semiconductor technology or actually reverse the world order in the semiconductor industry?

When Pat Gelsinger, the chief executive of U.S. chip giant Intel, visited Europe this spring to scout potential locations for a new factory, officials rolled out the red carpet. European nations are aiming to use part of a 145 billion euro digital fund — about \$175 billion — to finance chip investments and double <u>their share of worldwide chip manufacturing</u> by 2030, to 20 percent of the \$540 billion global market.

https://www.reuters.com > technology > taiwan-minister-s...

#### Taiwan's chip industry set for years of growth: minister | Reuters

Apr 23, 2021 — He said between now and 2025, **Taiwan** companies have planned more than T\$3 trillion (\$107 billion) in **investment** in the **semiconductor** sector, ...

Will this \$52 Billion investment by US Government close the gap that exists today in semiconductor technology or actually reverse the world order in the semiconductor industry?

https://www.industryweek.com > article > taiwans-tsmc-...

#### Taiwan's TSMC Plans \$100 Billion Investment to Meet Demand

Apr 5, 2021 — **Taiwan Semiconductor** Manufacturing Company said Thursday it was planning to **invest** \$100 billion over the next three years to meet soaring ...

South Korea became the latest country to announce a colossal investment in the industry last week. The nation's government said Thursday that **510 trillion South Korean won (\$452 billion)** will be invested in chips by 2030, with the bulk of that coming from private companies in the country. May 17, 2021

Samsung Group, South Korea's tech giant, announced on Tuesday that it will invest **\$205 billion (240 trillion won)** in their semiconductor, biopharmaceuticals and telecommunications units over the next three years to enhance its global presence and lead in new industries such as next-generation telecommunication and ... Aug 24, 2021

Will this \$52 Billion investment by US Government close the gap that exists today in semiconductor technology or actually reverse the world order in the semiconductor industry?

https://thediplomat.com > 2020/09 > can-china-become...

#### Can China Become the World Leader in Semiconductors?

Sep 25, 2020 — **China** appears on track to reach the **investment** level of \$150 billion in 2020 without having reached either of its stated long-term goals. And ...

Will this \$52 Billion investment by US Government close the gap that exists today in semiconductor technology or actually reverse the world order in the semiconductor industry?

Summary of Reported Investments by Some Key Players Timeframes of investments vary making comparisons sketchy

| US Government        | \$50 Billion                    |

|----------------------|---------------------------------|

| Intel                | \$100 Billion (over 10 years ?) |

| Európean Governments | \$175 Billion                   |

| Taiwan Government    | \$107 Billion                   |

| TSMC                 | \$100 Billion                   |

| Korean Government    | \$450 Billion                   |

| Samsung (included?)  | \$205 Billion                   |

| China                | \$150 Billion (in 2020 alone)   |

There are serious concerns in the US military that we will not be able to maintain state of the art military systems without domestic state of the art semiconductor technology

The lack of access to state of the art semiconductor technologies in most US universities is primarily driven by the lack of commitment by the US government to support these programs and to support the semiconductor industry to the level of support provided in some other countries

Input on re-establishing priority for governmental support of the US semiconductor industry is critical

Many companies around the world are still using 65nm to 0.5µm technologies for new designs and will for the foreseeable future

Extremely high volume applications of highly complex systems operating at high speeds drive the state of the art technologies

# **Stay Safe and Stay Healthy !**

# **End of Lecture 7**